RGB IP Core

北格逻辑 RGB 接口 IP 核能够从标准接口 AXI4-Streaming 不断读取数据驱动在 TFT-LCD 中显示。该IP核实现可变像素宽度(240/320/640)和 可变色深等级(RGB444/RGB565/RGB666)的 TFT-LCD 清晰动态画面稳定显示,普遍适用于多种分辨率图像切换显示,并且参数可动态配置。 该IP核占用资源较少,能够完成 TFT-LCD 显示时序及控制方面的要求且控制灵活,能驱动大部分的 TFT-LCD。 该IP核使用行业标准接口 AXI4-Streaming,北格逻辑 RGB 接口IP核是基于 FPGA 驱动 TFT-LCD 的一套较佳并且经济的解决方案,目前已在北格逻辑多个解决方案中使用。另外此IP可以轻松集成到您的 FPGA 设计中。

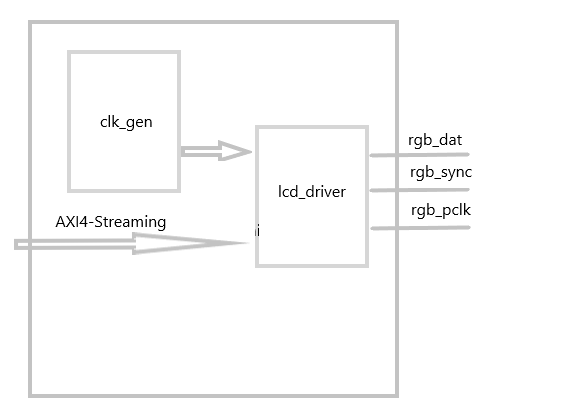

部分功能框图

部分功能框图

该IP核可支持不同分辨率以及不同帧率,常见可支持30fps/60fps, 内部会使用PLL锁相环生成所相匹配的像素时钟PCLK,用于计算行同步以及场同步信号来匹配相应时序。

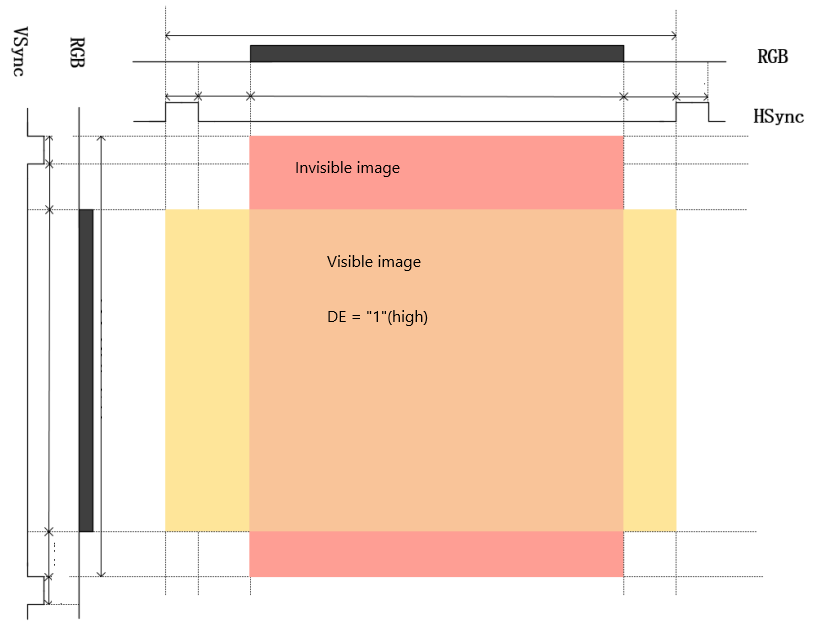

RGB接口时序

RGB接口时序

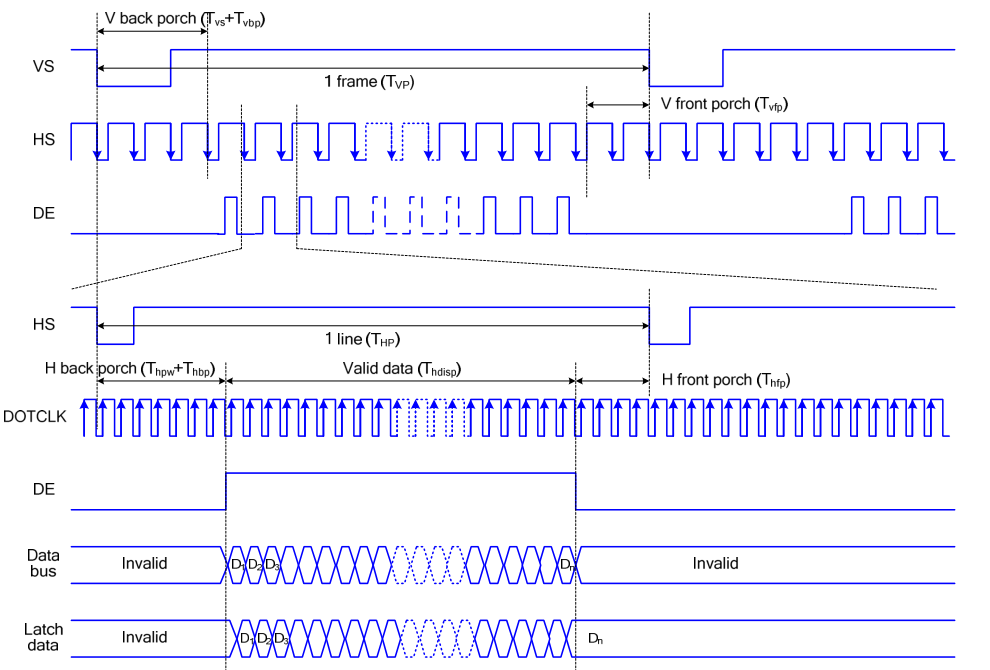

该IP核支持两种RGB接口,DE模式和HV模式,以及6bit/18位数据格式, 选择DE模式时,可以使用VSYNC、HSYNC、PCLK、DE、D[17:0]引脚; 选择HV模式,可以使用VSYNC、HSYNC、DOTCLK、D[17:0]引脚。 通过RGB接口的显示操作与VSYNC、HSYNC和PCLK信号同步。 数据在低功耗的指定区域内写入,后廊和前廊用于设置RGB接口时序。 以分辨率240*240为例,按照默认配置PCLK设置为9MHZ情况下,帧率可达70fps。

RGB接口同步时序

RGB接口同步时序

- • 支持320*240等多种不同分辨率

- • 支持RGB444/RGB565/RGB666

- • AXI4-Stream 视频接口

- • 支持常见帧率30fps/60fps等

- • 资源占用较少